直击前线科研动态

尽在芯片揭秘●科研前线

作为应用于下一代集成电路制造工艺的GAAFET器件结构,其多层堆叠的结构增大了刻蚀工艺的复杂性,相关参数的波动难以测量表征。IBM工艺研发团队通过先进算法与机器学习结合传统仪器测量发放,实现不通过对整个光学模型解析的计算求解路径,相关研究成果先行刊载于IEEE Transactions on Semiconductor Manufacturing。

各大晶圆制造厂商已陆续提出基于nanosheet沟道的GAA晶体管器件结构(以下简称GAAFET),GAAFET的栅极360°包裹nanosheet沟道四周,相比FinFET更能在器件尺寸缩小的同时改善静电控制。这样一个复杂的新结构引入显著增加了工艺步骤,也对新一代制造设备的改进提出了更多的要求。

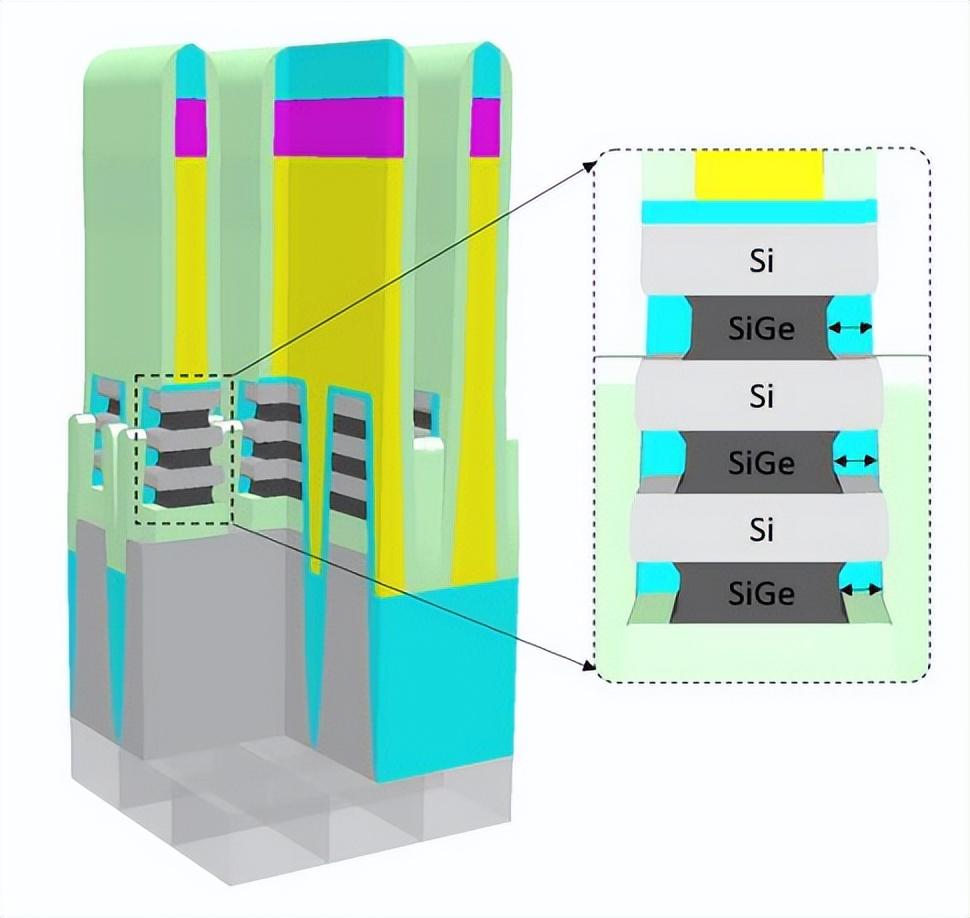

制造nanosheet GAAFET的一个关键工艺模块是内部间隔层的形成,它将沟道与与源/漏区域区分开来,并定义了栅长度。在完成内部间隔层的沉积的前一步关键步骤是横向蚀刻SiGe沟道的牺牲层。这种横向蚀刻步骤也称为cavity etch或压痕(indentation),蚀刻后的完整器件堆栈示意图如下图所示。

如果内部间隔层刻蚀过深,栅长和器件性能会受到影响;如果刻蚀太浅,在SiGe去除工艺环节,太薄的内部间隔层可能不足以形成隔离屏障以保护源/漏极区域。除了典型的工艺参数和统计变化外,内间隔层蚀刻过程还取决于SiGe沟道的组分和厚度。然而传统的基于模型的计量技术很难准确地量化横向刻蚀量,因为与缩进过程挂钩的体积变化幅度非常小,难以测量——具体来说一个单元内的体积变化仅为1%左右。

针对这一工艺难题,IBM研发团队设计了不同的表征方法测量相关参数,其成果以Development of SiGe Indentation Process Control for Gate-All-Around FET Technology Enablement为题发表于IEEE Transactions on Semiconductor Manufacturing,Daniel Schmidt为第一作者及通讯作者。

IBM研究团队采用多种非破坏性、并行兼容的计量方法以表征SiGe nanosheet沟道侧向纳米压痕,具体研究内容包括:

· 制备三种由不同组分的SiGe牺牲层构成的GAAFET器件;

· 采用不同的刻蚀工艺环境以引起压痕深度的变化;

· 通过干涉光谱法和X射线荧光分析法相结合的散射测量,辅以机器学习算法以量化SiGe纳米压痕测量;

· 给出了平均缩进和sheet沟道缩进两种方法的解;

通过机器学习算法通过将荧光分析法测量差值数据与散射光谱相结合,实现了快速求解路径,从而避免了对全光学模型求解的需要;最终结果显示,光谱干涉散射法和传统光学模型结合先进的算法,可以实现与sheet沟道相关数据的良好匹配。

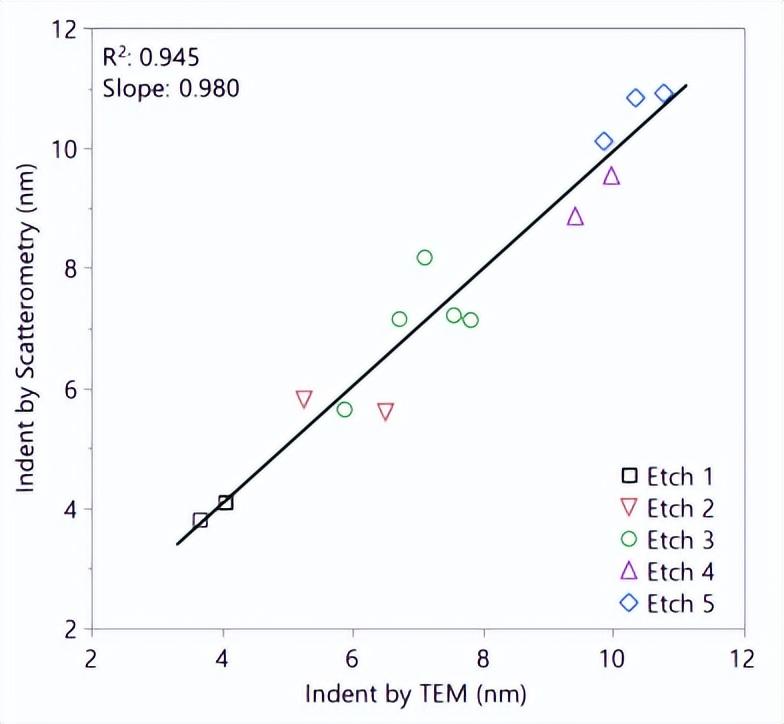

散射法和TEM测定SiGe压痕的比较

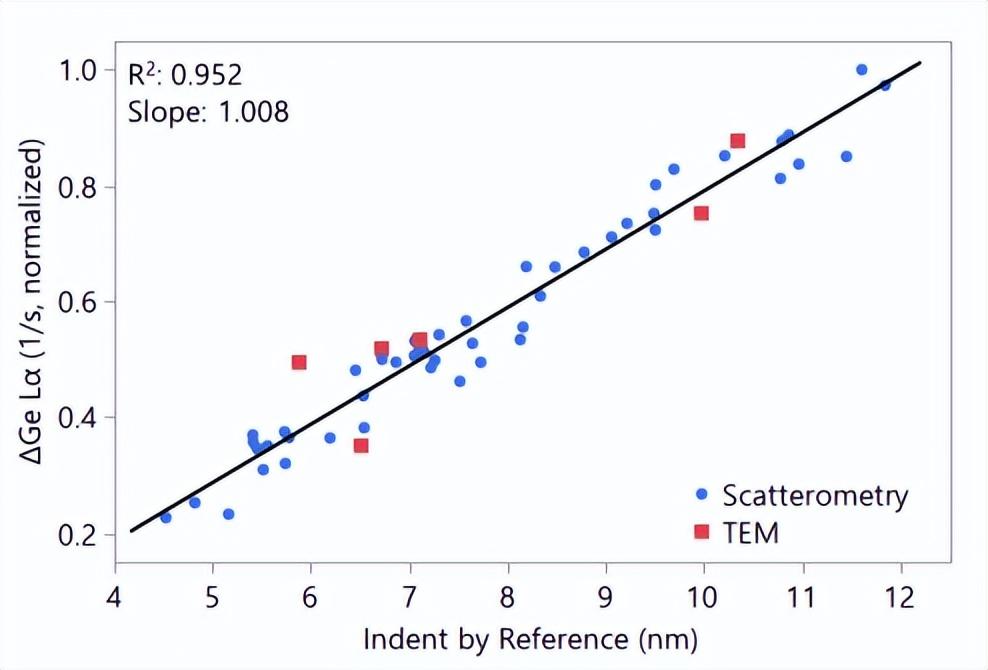

通过归一化的△Ge Lα作为函数表征 散射法和TEM的基准数据 △Ge Lα:表示刻蚀前后的Ge组分X射线测量结果

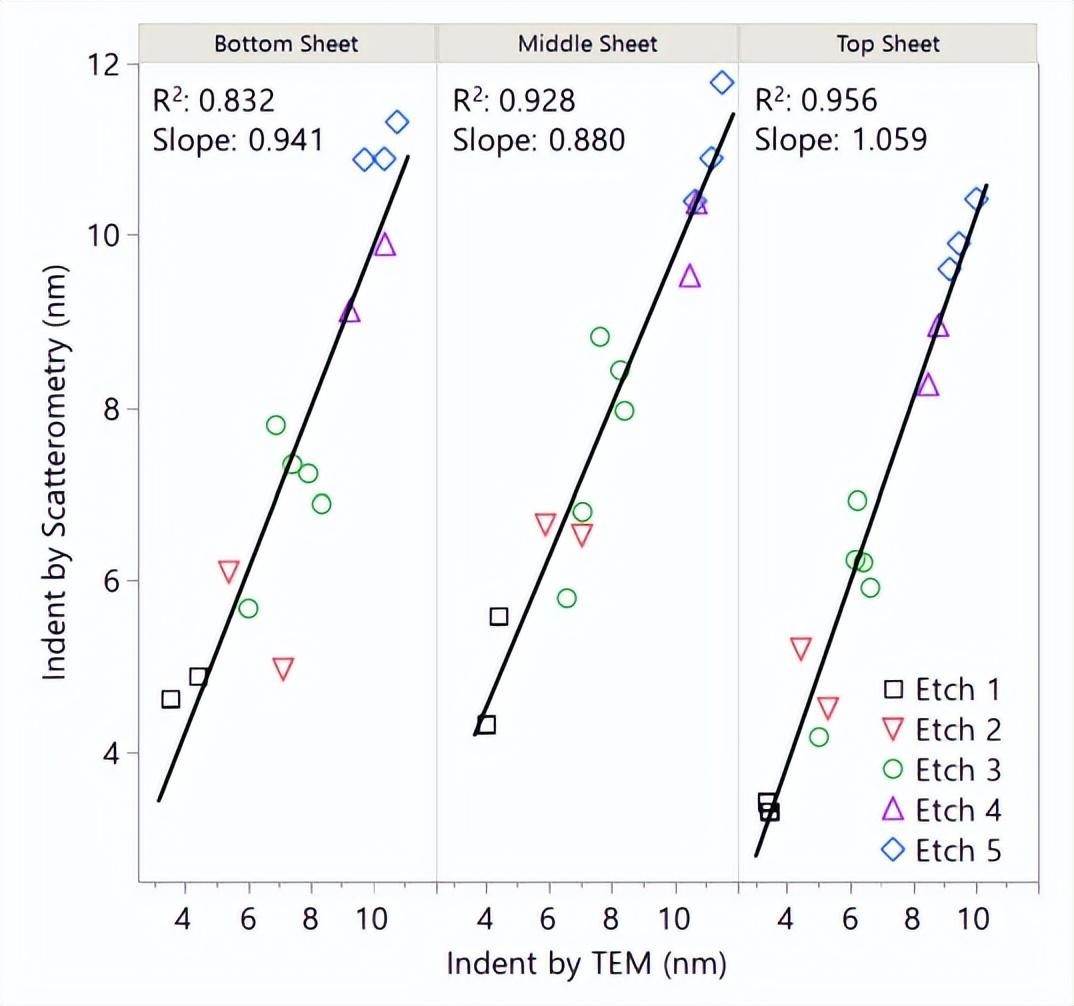

基于TEM图像分析、通过散射法测量获得的 压痕分布函数 三个坐标图分别表示沟道底部、中部和顶部的测量结果

IBM所开发的侧向压痕检测方法与高通量散射测量相结合,整合了两种方法的优势,为工艺开发阶段和规模量产阶段的工艺流程监测提供了更理想的解决方案:在工艺开发阶段,晶圆工艺层堆栈的设计可能随时变动,这是首选具有高级解释算法的传统模型;当工艺原型确定、进入规模量产阶段,通过足够多的横轴参考数据来训练机器学习模型更具效益。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。