直击前线科研动态

尽在芯片揭秘●科研前线

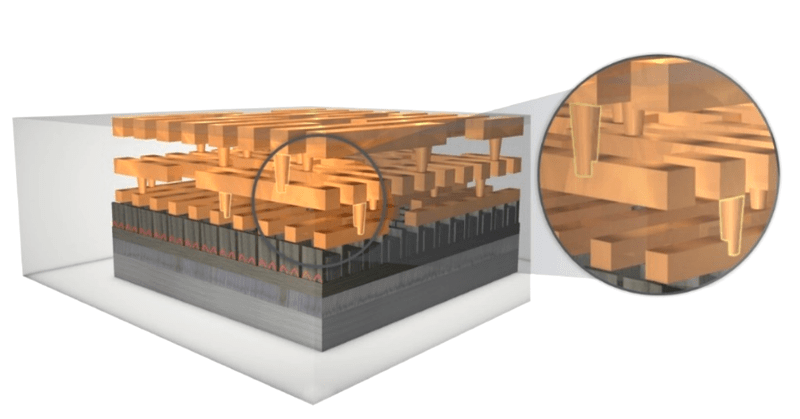

最新一届IEDM会议论文近日已公开,集成电路制造龙头台积电发表了多篇有关先进工艺的研究成果,其自对准通孔SAV工艺,在电特性、器件可靠性和良率方面均有良好表现,将是其保持行业龙头地位关键研究之一。

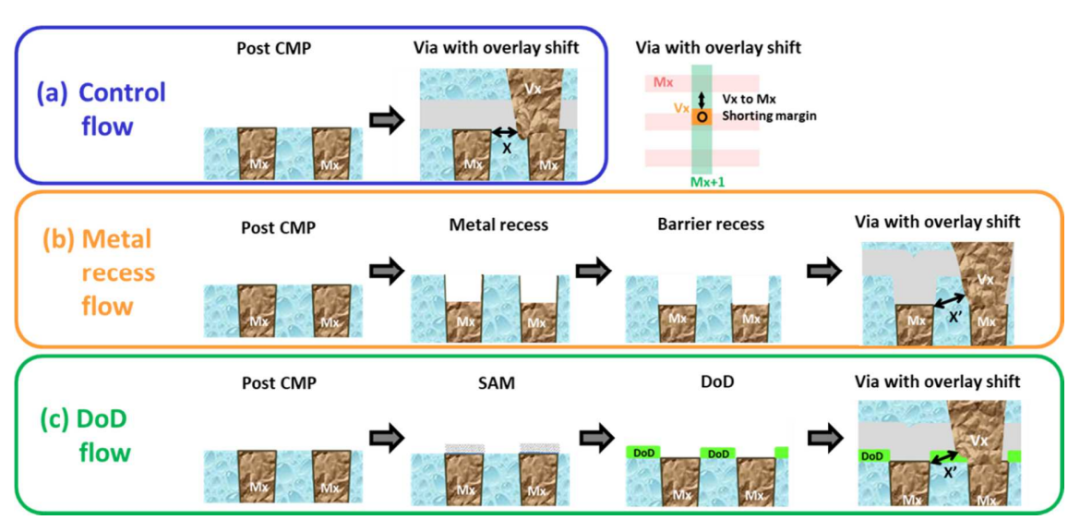

在先进的节点中,特征尺寸变化和边缘放置误差(EPE)*是3nm以下工艺节点中互联层微缩环节不可避免的工艺难题,它们导致漏电和可靠性。为克服这一挑战,发展了多种方法来形成SAV自对准通孔,包括金属线凹进和蚀刻阻挡层的选择性沉积工艺等。基于SAV的湿法金属凹陷和阻挡层提出的工艺方案,可以增加孔-线间隙,提高TDDB(经时介电层击穿)和通孔关键尺寸控制。

作为集成电路制造的引领者,台积电也在布局这一前沿领域,相关成果以Fully Self-Aligned Via Integration for Interconnect Scaling Beyond 3nm Node为题发表于2021年IEEE国际电子器件会议(IEDM),H.P. Chen为第一作者及通讯作者。

*边缘放置误差,Edge Placement Error,是光刻软件仿真出的曝光后光刻胶图形边缘与设计图形之间的差,见下图图示。

台积电工艺研发团队研究两种方案全自对准通孔SAV工艺,分别通过金属凹陷法和面积可选择性电介质上电介质(DoD)实现。其主要研究内容包括:

发现布线流程中更大对角距对于自对准工艺的重要影响;

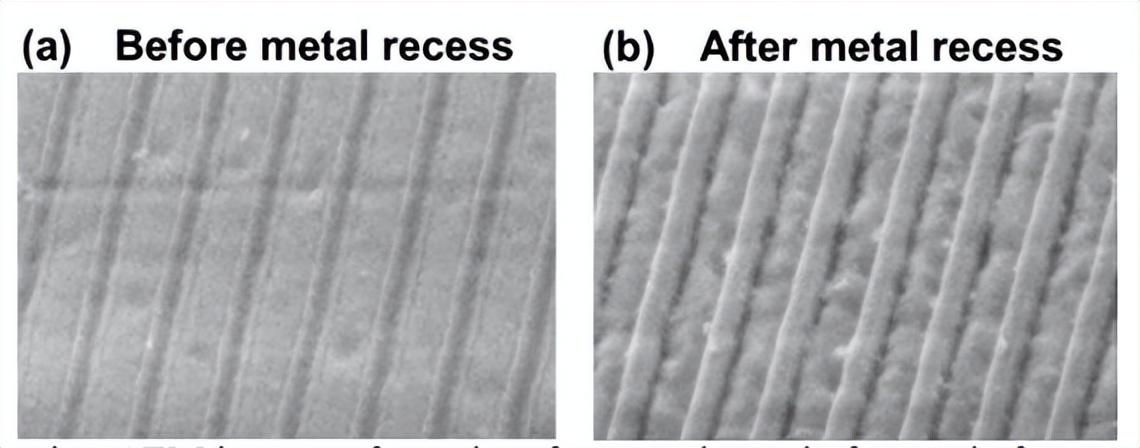

金属凹陷工艺存在均匀性差、表面粗糙度高、金属完整性(metal integrity)衰减等问题;

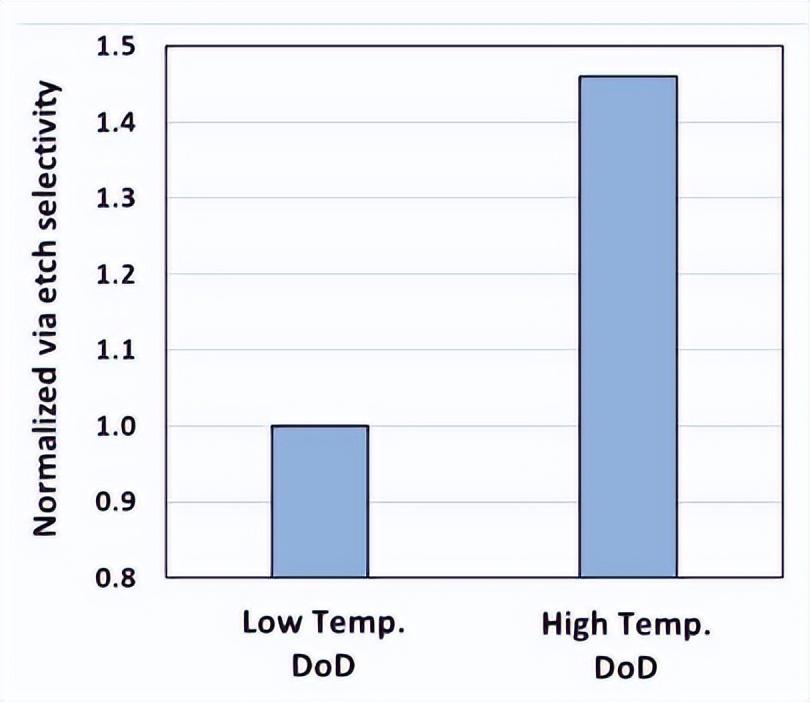

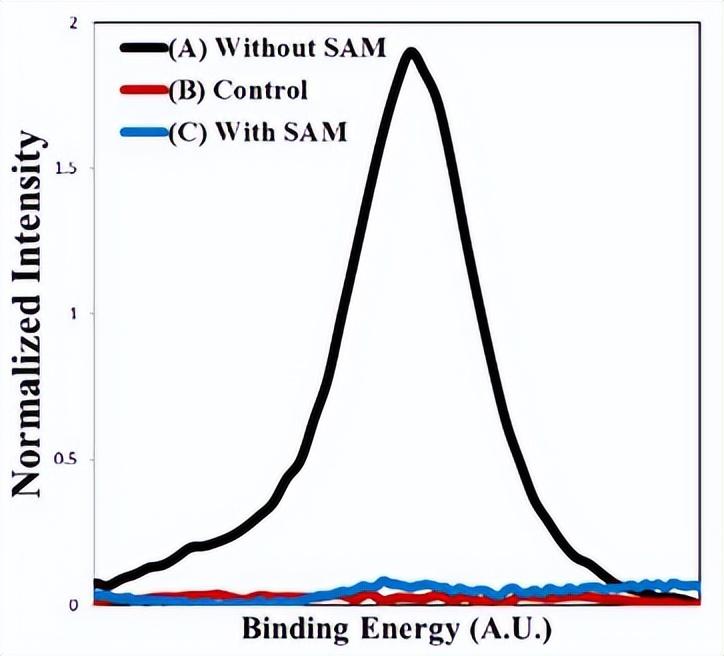

DoD工艺通过采用选择性自组装单层阻挡材料,实现了向上越阶电介质沉积的工艺,并展示出高达两个数量级的经时介电层击穿的改善;

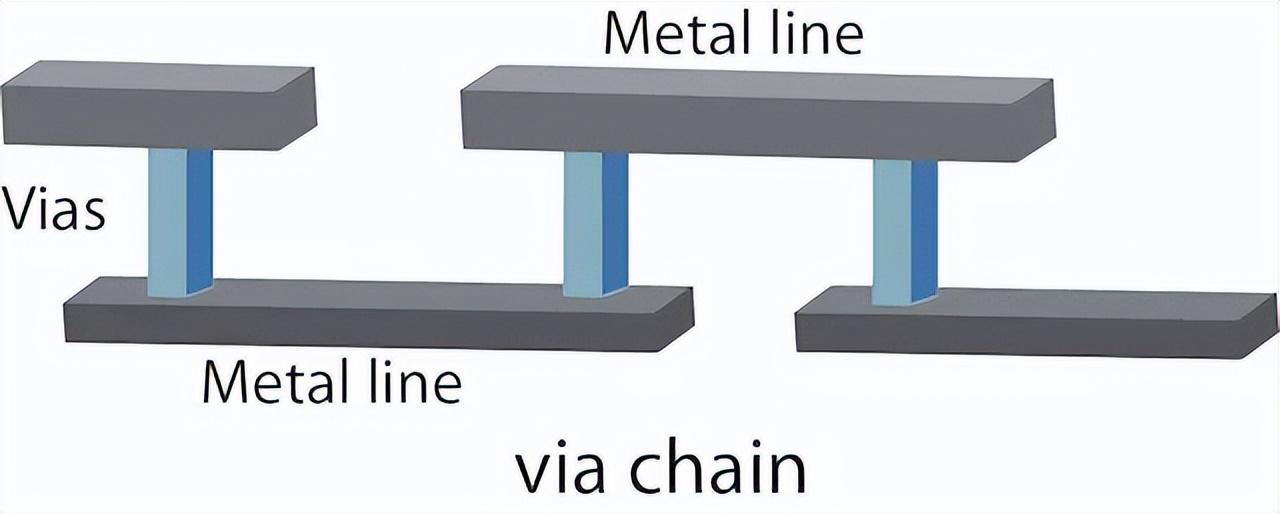

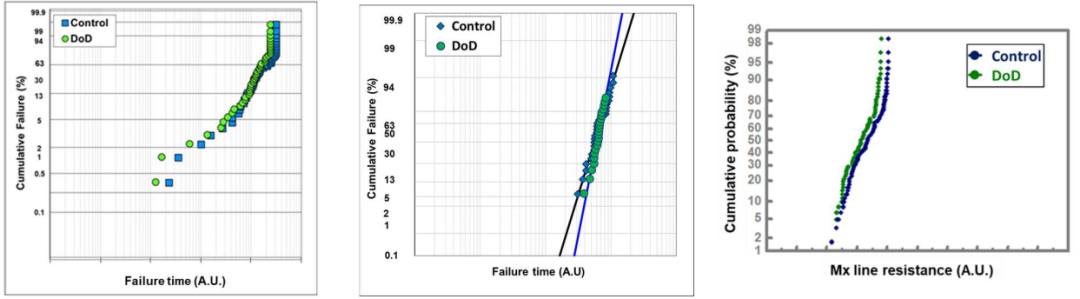

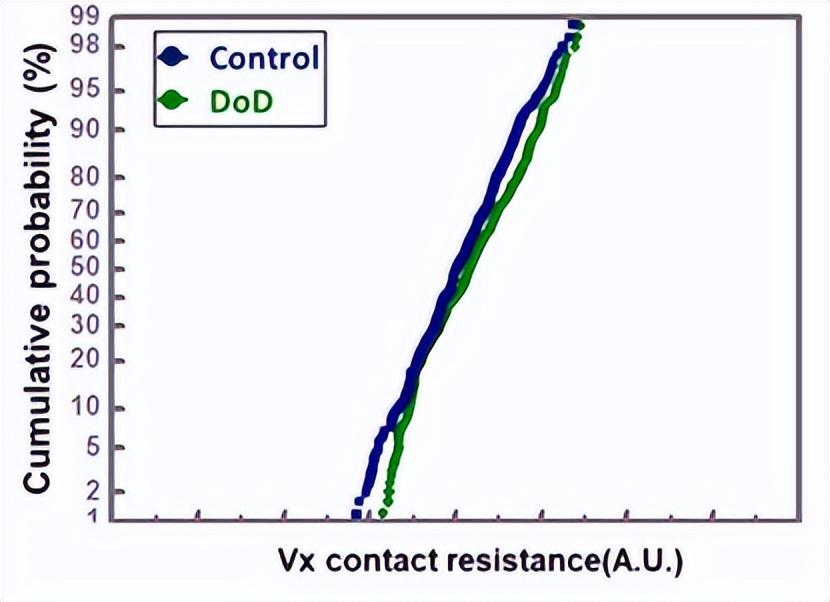

对DoD工艺在孔-线电阻、via-chain(见下图)良率、金属线TDDB和EM可靠性的表现进行测试,达到了量产水平。

via-chain结构示意图 (图源:techdesign)

工艺流程示意图

高低温下的通孔刻蚀可选择性对比

金属表面粗糙度SEM形貌像对比

DoD信号在三种沉积方法下的X射线能谱

金属线间TDDB寿命(左)、EM寿命(中) 以及金属线电阻(右)

通孔接触电阻变化曲线

研究团队通过评估2.5、D封装、两种FOCoS封装这三种异质集成封装的力学性能和热性能,验证了有限元模型的有效性,并且通过比较发现FOCoS相比2.5D封装具有更好的电气性能与热性能,在热膨胀错配和散热方面表现良好,日月光也对该技术替代硅中介层解决方案的寄予厚望,相信未来能在丰富的应用领域占有一席之地。

台积电研究团队实现了可应用于亚3nm工艺的线路互连微缩,具有低金属线电阻、通孔电阻和高良率的优势,可预见将在未来进一步助力台积电3nm、2nm工艺的成熟落地,为其集成电路制造龙头地位保驾护航。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。