直击前线科研动态

尽在芯片揭秘●科研前线

近日,复旦大学与华东师范大学联合研究团队发表了关于DCTO协同优化技术的研究成果,通过对于MOEL/BOEL环节的后端优化评估方法存在的问题进行改进,提出了新的DTCO优化流程,并通过测试得到了最佳PPA的nanosheetFET模型。

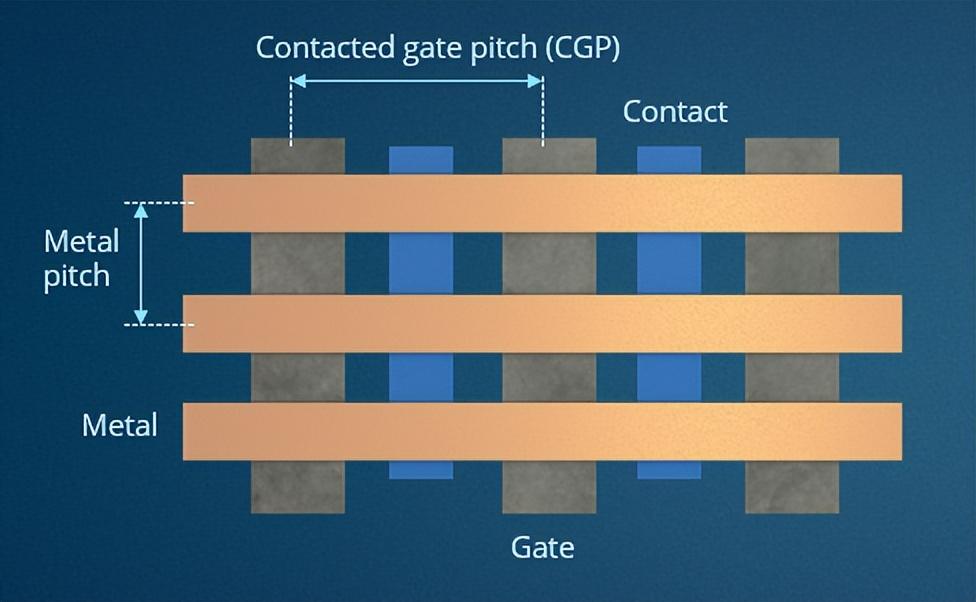

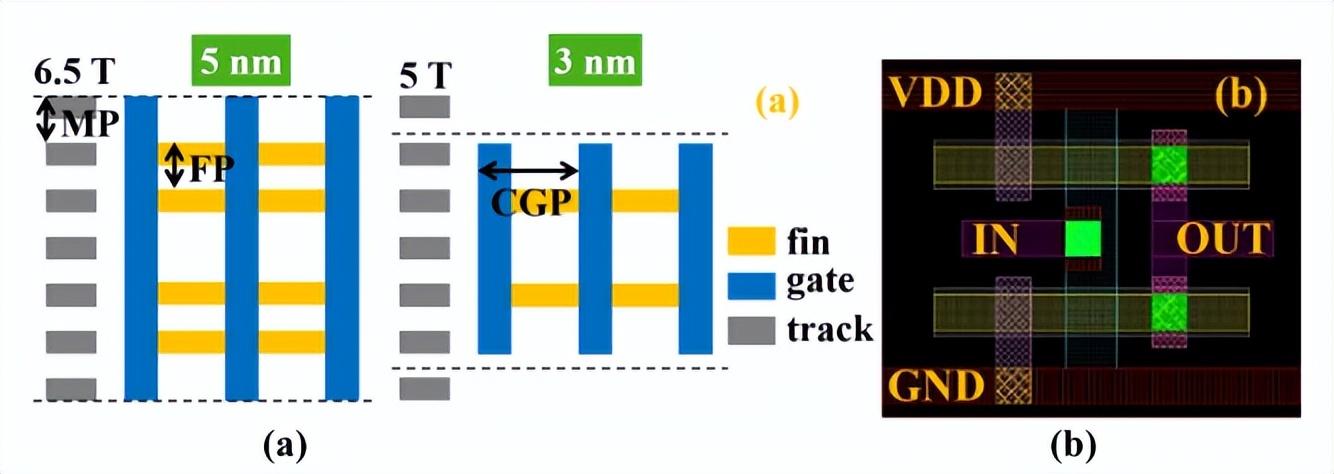

随着集成电路晶体管特征尺寸的持续缩小,新型器件结构也面临着不同的性能瓶颈。以nanowire或nanosheet作为沟道形状的GAA晶体管(以下简称GAAFET)由于其理想的栅极静电特性和更好的功耗-性能平衡,已被广泛认为是下一代集成电路制造技术核心的器件结构,目前业界正在努力推进其研发量产进程。对于基于GAAFET的逻辑电路设计而言,标准单元尺寸主要取决于CGP*和FP*两个间距。

为降低标准单元尺寸同时满足芯片PPA(功耗、性能与面积)设计要求,基于TCAD的DTCO得到了很大的发展,已成为先进工艺中必不可少的环节。在DTCO中,综合考虑工艺、晶体管结构和电路设计目标,在优化过程中计算和反馈电路PPA,通过技术参数的调整使工艺与电路设计相适应,实现最佳的电路性能。目前基于TCAD的DCTO包括FEOL工艺仿真、等效电路模型参数提取、MOEL/BOEL互连寄生参数提取、benchmark电路仿真等流程。

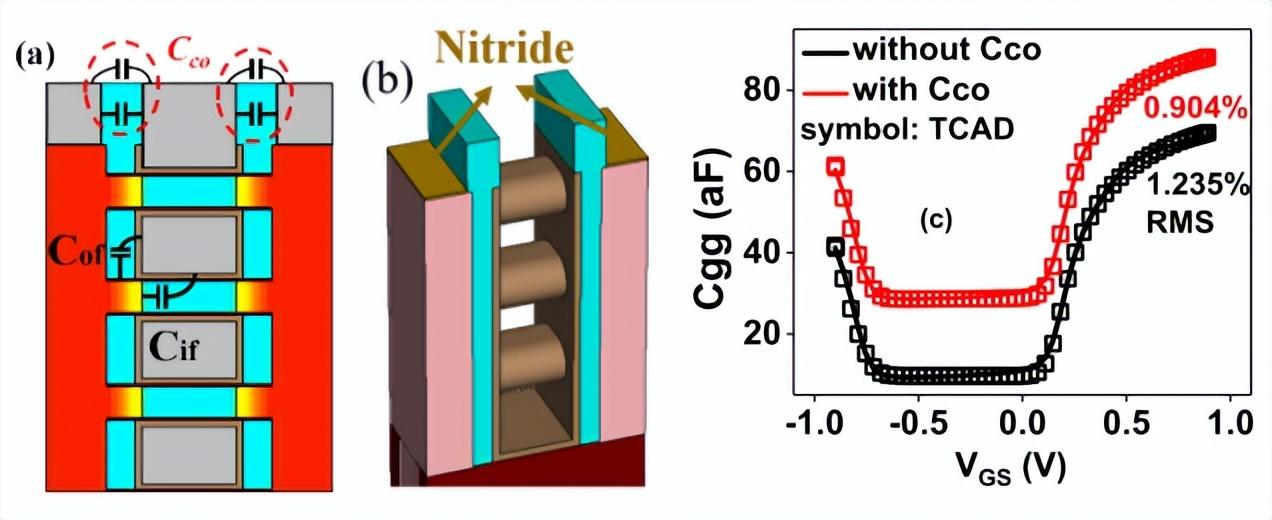

但上述估计方法存在两个明显的局限性:第一点,对于任意工艺节点,假定的等效长度并不总是保持不变,尤其对于BEOL环节来说,其金属电阻率对于工艺参数相当敏感;第二点,假定的等效BEOL长度可能与SPX模拟提取的电容参数不匹配。在前述的DTCO流程中反复提取栅源/栅漏接触电容Cco,也会不可避免地会影响模拟结果的准确性和可信度。

为克服上述问题,复旦大学与华东师范大学联合团队设改进的BEOL和MEOL参数的评估方法,其研究成果以“Improved MEOL and BEOL Parasitic-Aware Design Technology Co-Optimization for 3 nm Gate-All-Around Nanosheet Transistor”为题发表于IEEE Transactions on Electron Devices,孙亚宾为第一作者,刘子玉为通讯作者。

*CGP,全称contacted gate pitch,暂译为接触栅极间距,下图中已标出。

*FP,全称fin pitch,即FinFET中相邻Fin的距离。

图源:Applied Materials

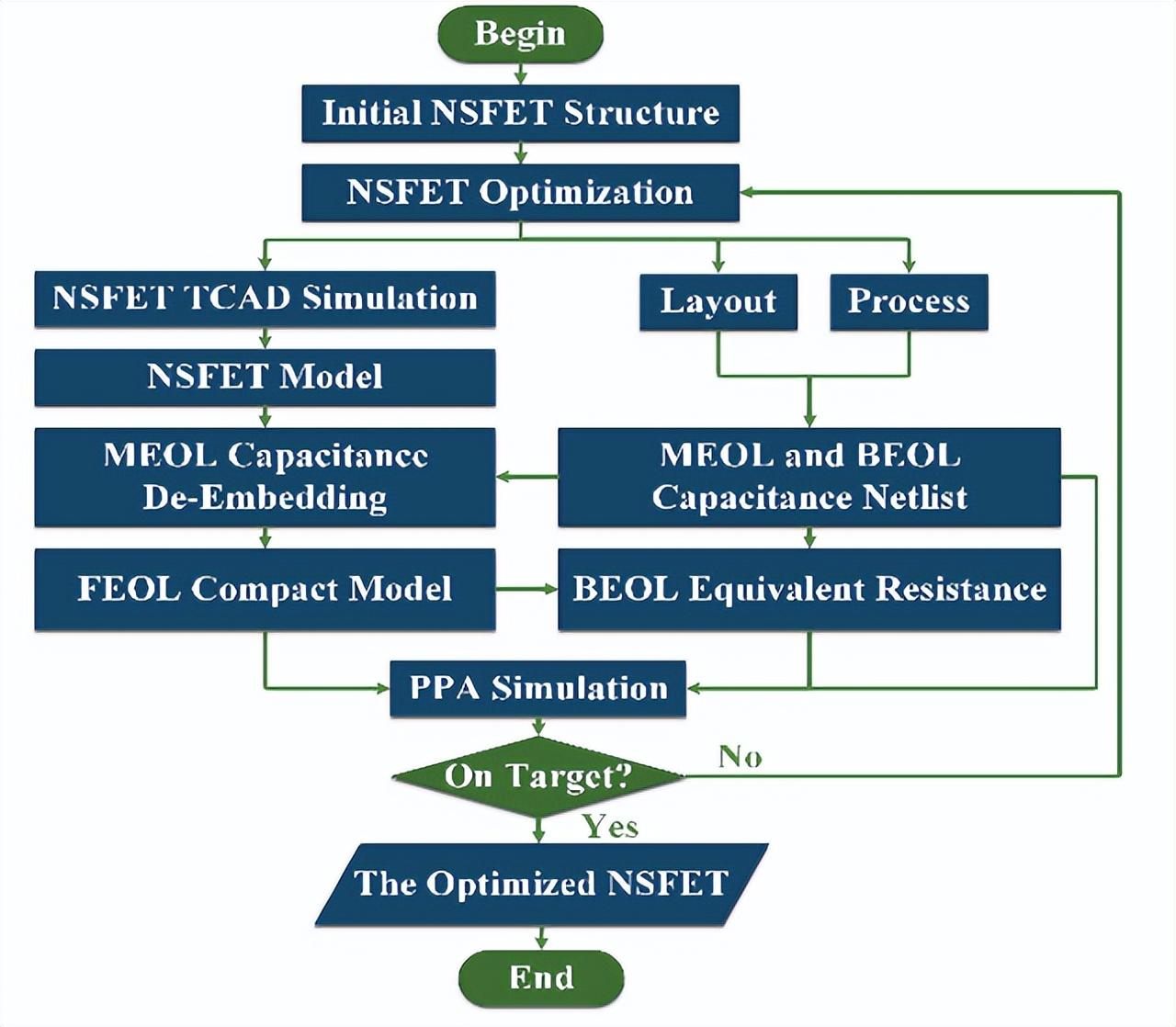

研究团队提出了一种改进的DTCO流程,重新设计去嵌入方法以避免重复计算栅源/漏极接触电容,并给出了一种用于3nmGAAFET节点的BEOL和MEOL电阻的评估方法。

具体工作包括:

· 基于BSIM-CMG模型对FEOL环节的电子特性进行了描述;

· 根据版图和工艺流程提取了互连寄生电容的netlist;

· 提取和去除了FEOL CM中重复的接触电容和电容网表;

· 利用所提出的等效仿真方法,提取了BEOL等效寄生电阻;

· 考虑CGP的限制和结构对工艺的影响,通过提出的DTCO流程对nanosheetFET器件尺寸进行权衡优化;

· 以RO作为benchmark测试电路,得到了面积降低46%、功耗降低48%、频率提高26%的最佳nanosheetFET模型。

本文中应用于3nmGAAFET工艺节点的DCTO流程

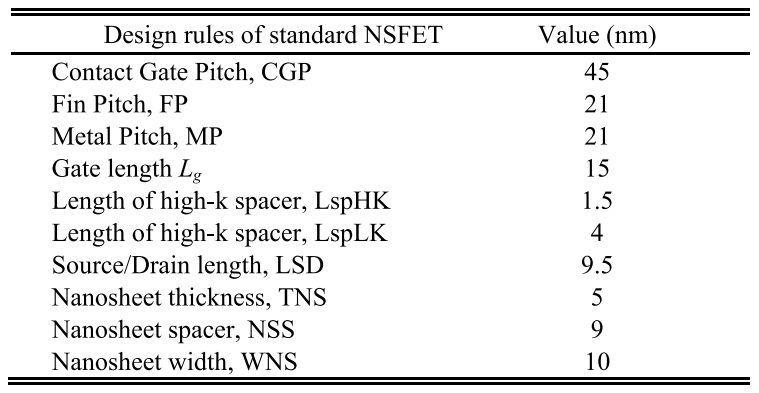

器件主要尺寸参数

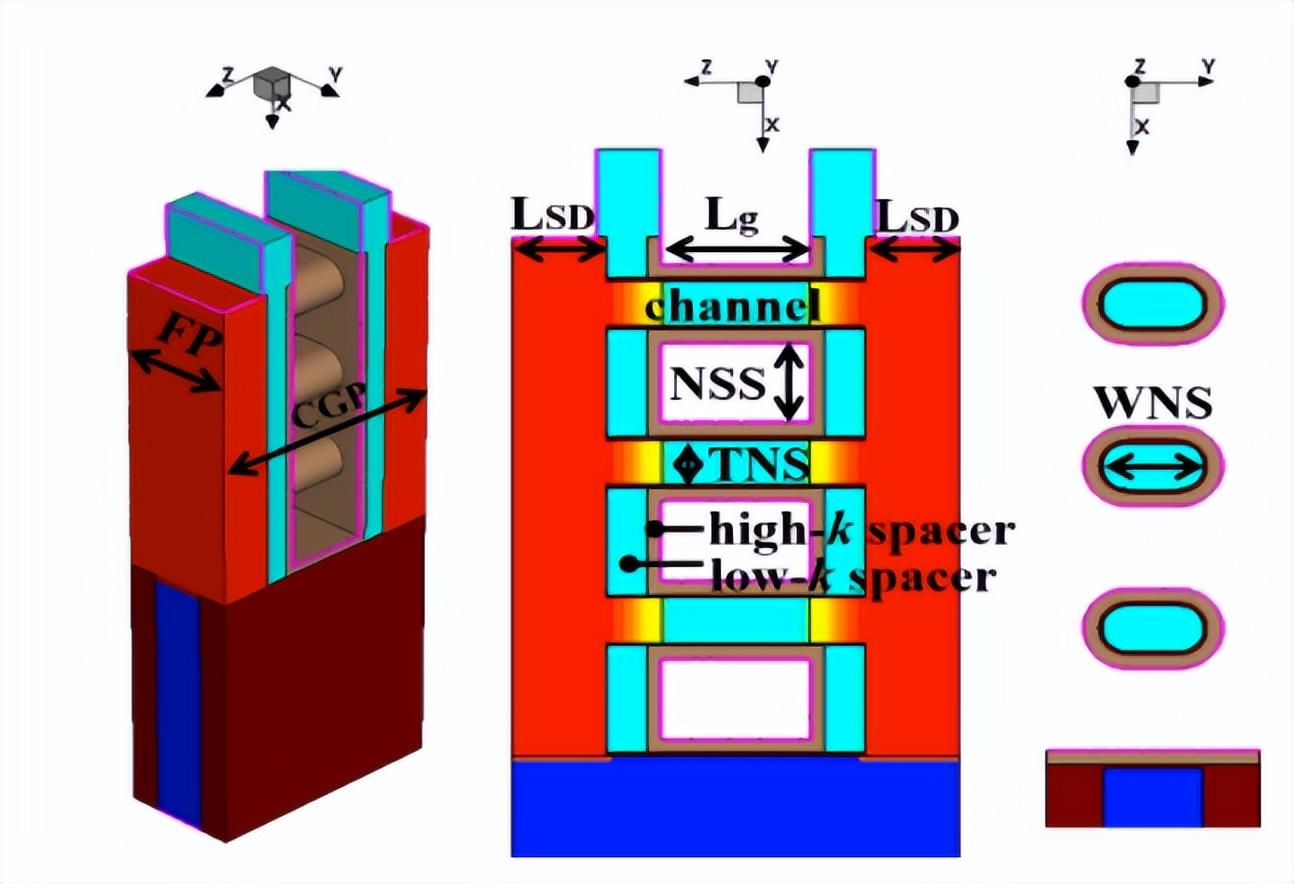

器件结构示意图

图(a)5/3nm标准单元版图; 图(b)单级反相器版图

图(a)nanosheetFET中寄生电容示意图; 图(b)寄生电容的仿真模型示意图; 图(c)两种建模仿真曲线比较

本项研究中,复旦大学与华东师范大学联合团队针对MEOL/BEOL环节的建模仿真和评估方法进行改进并针对多项关键参数进行研究,得到了相对理想的GAA nanosheetFET器件结构。这一研究发展了先进工艺节点的前沿研究,为技术节点协同优化技术的提供了良好的基础,后续系列研究也将有助于推动GAAFET器件的设计研究与工艺发展。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。