直击前线科研动态

尽在芯片揭秘●科研前线

研究背景BRP与CFET器件结构等前沿技术未来将落地先进节点,结构的改进使得集成电路内部的自热效应增强,与之相关的HCI等可靠性问题难以忽视。北大杜刚团队在2021年中的SNW研讨会发表的CFET自热效应成果基础上,进一步研究了热串扰和相关可靠性问题,其研究成果刊载于IEEE TED一月刊。

集成电路先进工艺的发展进度日趋放缓,IMEC提出在5nm以下节点应用BPR*技术,业界预测三星、台积电等IC制造商会在2nm/3nm节点应用;而作为FinFET器件结构继任者的GAA nanosheet FET也被普遍认为在两次大节点迭代后会面临进一步的结构创新,基于“折叠”思路的CFET便是GAA环栅结构的进阶版本,该技术路线已被主要IC制造商接受并纳入了研发规划中。

与在二维平面上排布晶体管的传统CMOS工艺相比,垂直堆叠的CFET结构使标准单元面积减少了50%,而电气性能没有降低,但全三维结构使得其散热效果不容乐观。更有甚者,可能会造成上下p/nFET之间发生严重串扰,从而加剧发热问题。

集成电路中的SHE(Self-Heating Effects,自热效应)严重影响器件的电气特性和可靠性,随着技术节点尺度缩小,晶格中声子边界散射不断增强,易生成局部热点导致晶格温度升高。随着工艺引入材料和拓扑结构的等微创新,材料内部的散热路径被极大的限制,增加了设备之间的热串扰。以上种种随着结构创新而更加严峻的散热问题将对HCI、BTI、EM电迁移等可靠性问题造成巨大挑战。

北京大学微纳电子学研究院杜刚团队在针对CFET热效应研究课题中针对上述问题进行相关实验,研究成果以“Self-Heating and Thermal Network Model for Complementary FET”为题发表于IEEE Transactions on Electron Devices,赵松涵为本文第一作者为,杜刚教授为通讯作者。

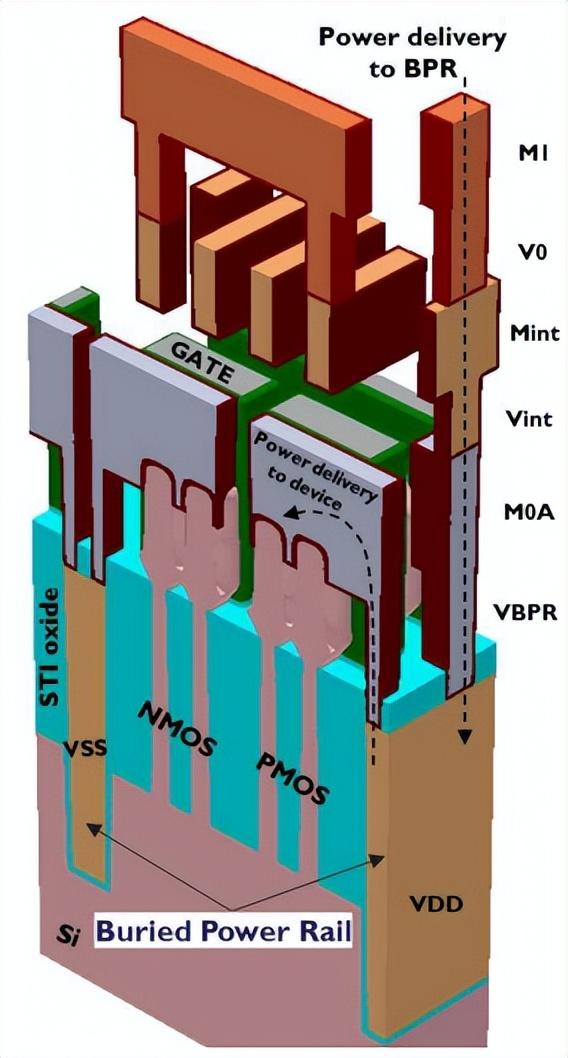

*BPR,全称Buried Power Rail,即在晶体管下方埋入电源线的构造(见下方示意图左,图源imec)。

*CFET,全称Complementary Field Effect Transistor,通过在垂直方向实现nFET与pFET堆叠的3D晶体管结构(见下方示意图右,图源imec)。

图为BRP与CFET示意图

在之前的研究中SNW发表的成果中,团队研究了CFET晶体管的热量分布;本次,研究团队为模拟CFET的热行为,通过定义串扰系数评价了器件内部和器件间的串扰程度。结果表明,CFET器件内部的热串扰是标准CMOS器件的两倍。

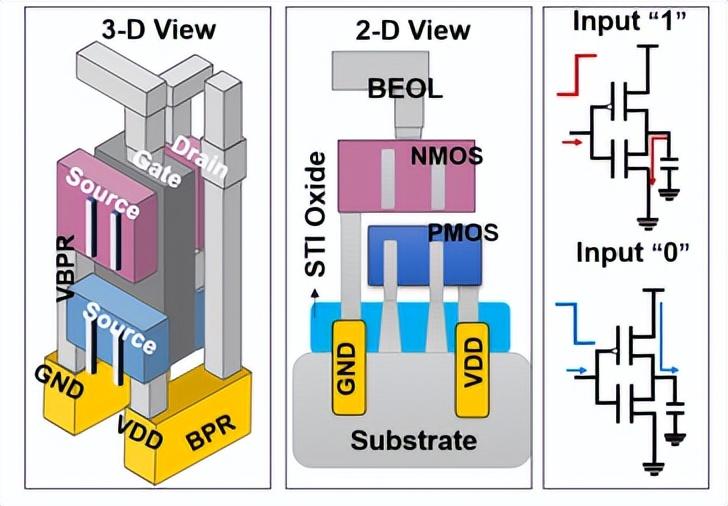

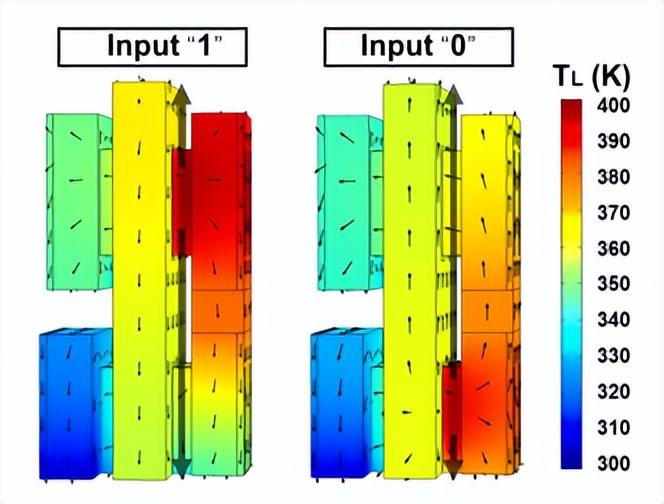

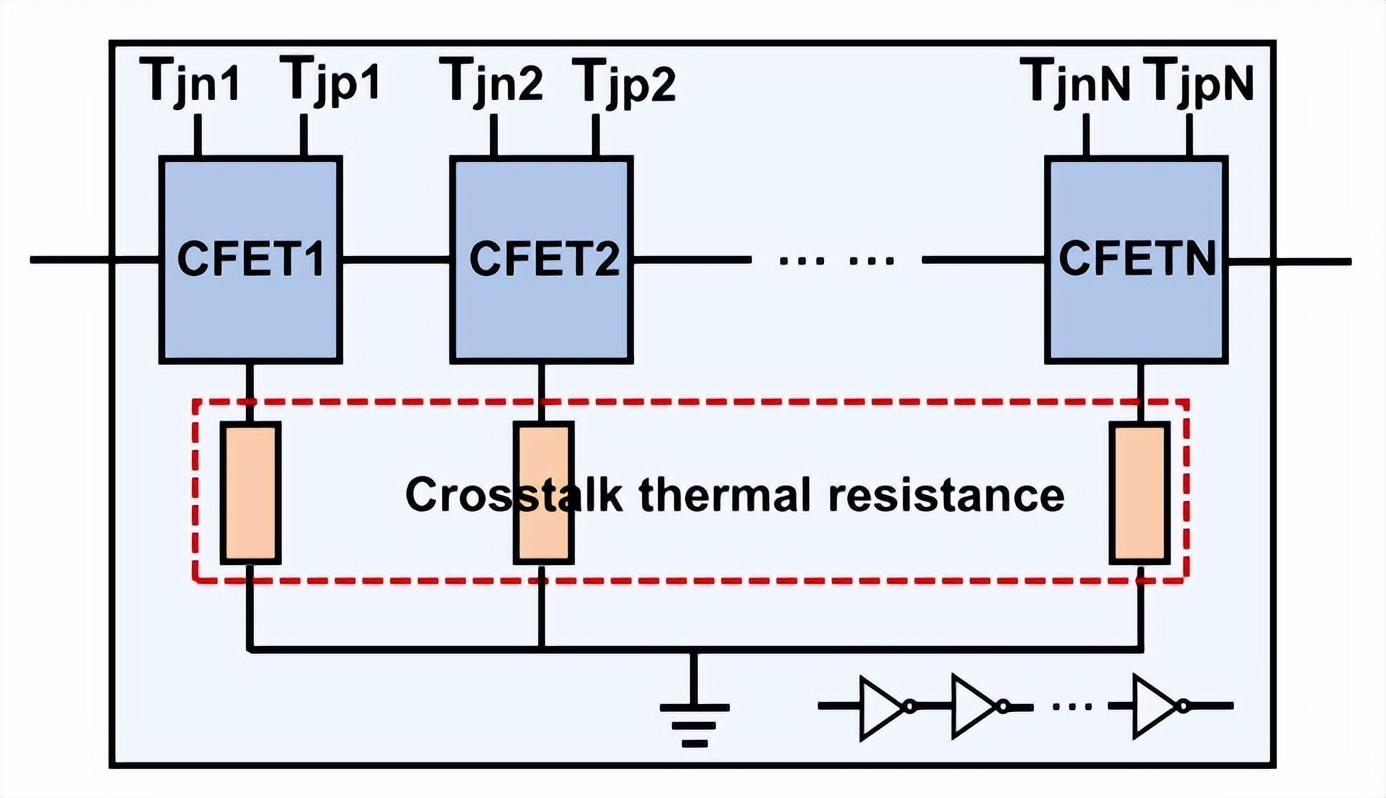

此外,垂直结构使得CFET器件在两种输入状态下呈现截然不同的散热路径,基于CFET的热运动特征和必要的高精度快速预测设备的热特性,团队提出了一种热网络模型,它可以快速响应热源并实现阵列级电路扩展。

最后,团队分析了负载电容和工作频率对自热的影响,并根据热网络阵列温度预测了与SHE相关的可靠性寿命。预测结果表明,CFET的偏温不稳定性(BTI)寿命比标准CMOS器件降低了84%。

CFET结构示意图与电路图

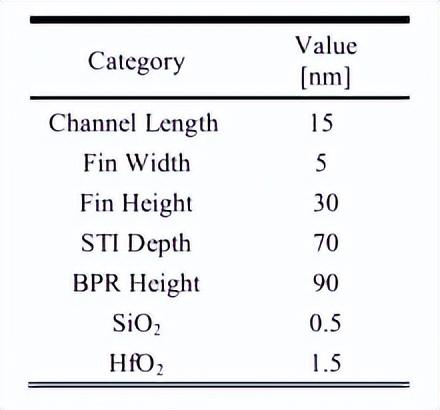

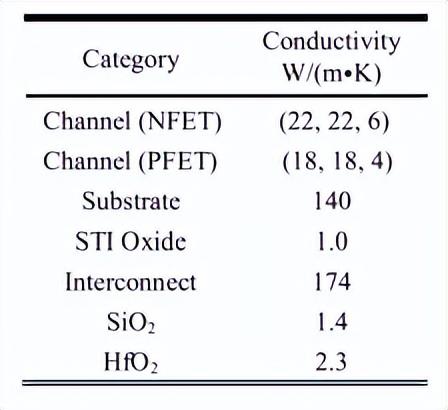

器件结构参数与热参数

不同输入状态下的热分布图

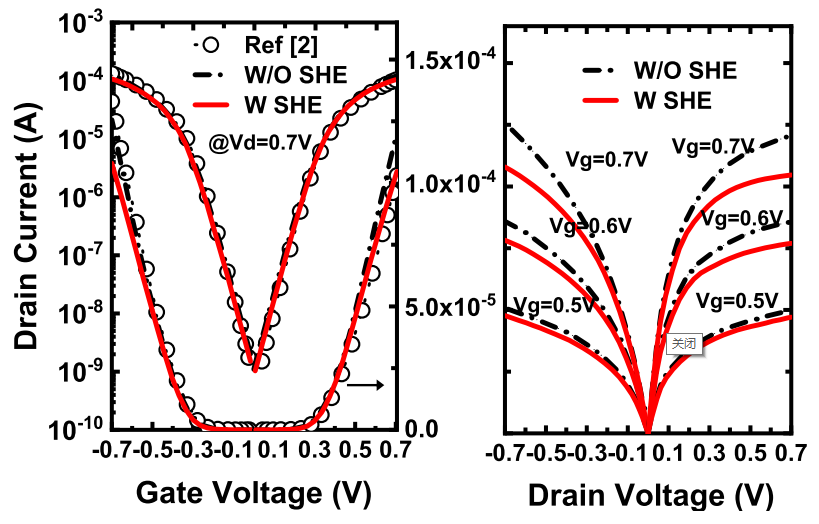

有/无SHE影响下的Id-Vg特性曲线

用于反相器链温度预测的阵列级热网

北大微电子团队在CFET器件自热效应研究上不断拓展,在热特性与可靠性评估模型建立寄出上,进一步量化测试了CFET自热效应,探究了先进工艺创新和器件结构升级过程会出现的热效应和可靠性问题,为CFET工艺的先导研究提供了更多地前沿技术基础。

杜刚教授,北京大学微纳电子学研究院教授,目前主要从事纳米尺度集成电路自热效应及可靠性、3D NAND存储阵列器件及电路可靠性以及纳米新器件中的输运现象,建立了新材料三维全能代MC器件模拟平台等器件模拟工具。

杜刚教授作为骨干人员先后参加多项国家973子项目、863项目、国家自然科学基金项目,负责一项国家自然科学基金科研项目。在器件模型模拟领域取得了大量创新成果,在国内外期刊和国际会议上发表论文200余篇。

北京大学微电子学研究院,是我国高水平微电子科学技术研究基地和微电子人才培养基地,研究院缘起上世纪五十年代由著名物理学家黄昆院士领导的在北京大学物理系创建的我国第一个半导体专业。在我国著名的微电子学家王阳元院士、黄如院士的领导下,北京大学微纳电子学科为我国微电子产业培养了大批优秀人才,是我国培养高水平微电子人才的一个重要基地,是国家和学校大力支持和发展的重点学科。

北京大学微纳电子学系下设5个研究所/中心和3个实验室:新器件及集成技术研究所(ULSI)、集成电路与系统设计研究所(SOC)、集成微纳系统研究所(MEMS)、宽禁带半导体研究中心、射频与太赫兹集成技术研究中心,以及IC CAE(EDA)实验室、工艺实验室和测试实验室。科学研究和人才培养在基础研究、关键技术、应用开发3个层面上展开,已经取得了一系列具有国际先进水平的科研成果。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。