直击前线科研动态

尽在芯片揭秘●科研前线

先进封装技术已经越来越多地走入人们的视野,成为推动芯片产业发展的又一大驱动力,其中用于承载晶圆片的小小IC载板也多次与日本味之素携手成为产业热点。在11月东京举办的第21届IEEE封装制造技术会议上,欣兴电子发表了高密度混合载板研究成果,将助力先进封装技术进一步发展。

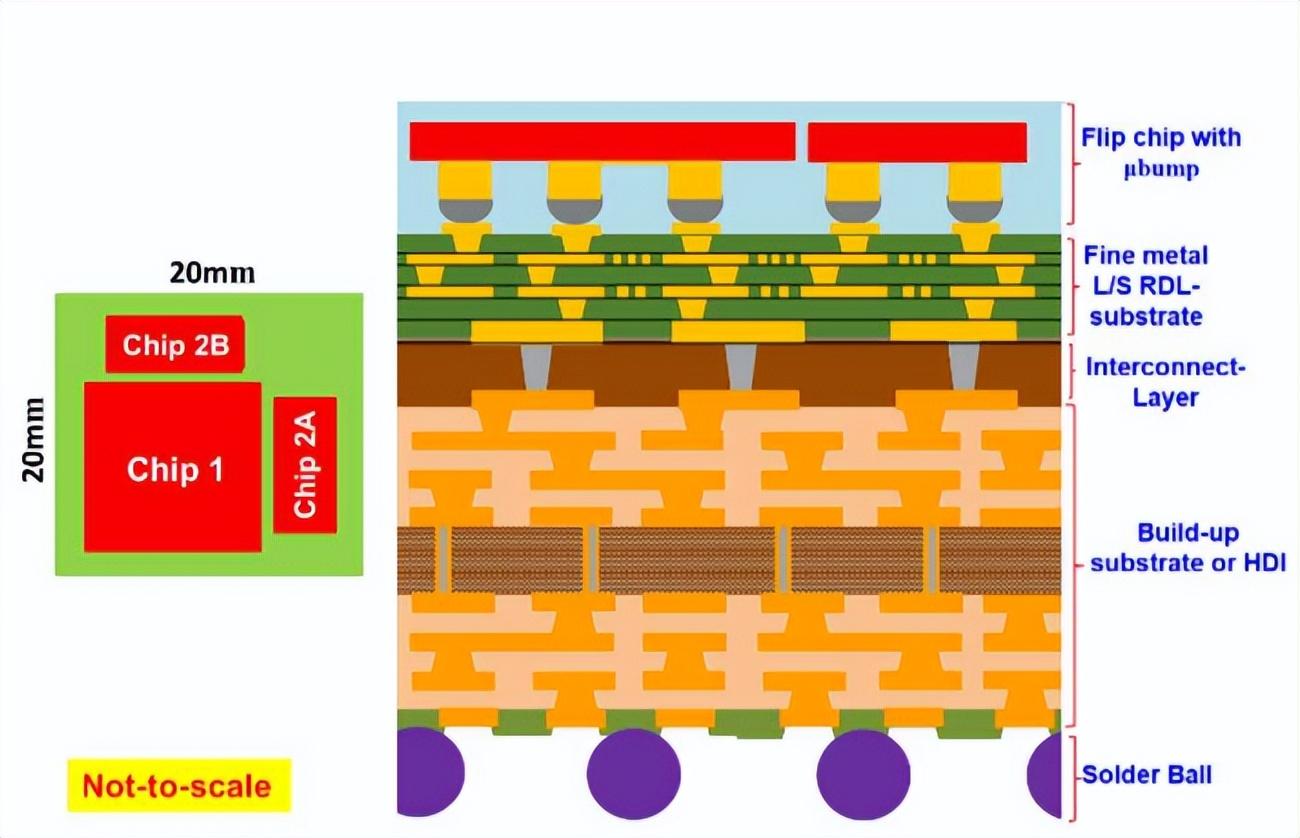

在摩尔定律逐渐放缓的当下,先进封装技术成为推动芯片性能进一步提升的关键因素之一。发展至今,先进封装已进行了多次迭代。在2.1D封装*工艺中,将具有细金属线宽和间距的薄膜层制备在积层(build-up)多层板的顶层,形成混合封装载板*;这种一次完成整个封装载板制备的工艺,其良率减损(暂译名,英文Yield Loss)不易控制,且程度较高。而在2.3D封装*中,用于承载晶圆片的硅中介层载板和用于焊接在电路板上的积层多层板则是分开制备、然后通过焊锡焊点进行互连,形成混合封装载板;这种工艺下,混合封装载板的良率减损更受控且程度更小。

在欣兴电子研究团队的研究中,与2.3D封装类似,将中介层载板和积层多层板或高密度互连PCB电路板*分开制作,然后通过互连层进行集成,但两者最大区别是本研究将原本2.3D封装中的焊点替换成了互连层,其研究成果以“Development of High-Density Hybrid Substrate for Heterogeneous Integration”为题发表于第21届日本封装与制造技术会议(IEEE CPMT Symposium Japan),第一作者为Chia-Yu Peng。

*2.1D/2.3D封装:2.1D封装主要指先进封装范畴中相对传统封装具有更高精度的晶圆级封装(WLCSP)和载板级封装(PLP);*2.3D封装,根据英文文献推测其类似(但不全等)中文互联网下通常指代的2.5D封装,即采用中介层的先进封装,其特点在正文中已有描述;通过TSV工艺实现垂直方向堆叠的封装技术则被称为3D封装。

*载板,即Substrate,在不同的集成电路细分领域中有不同的指向,此处指代芯片封装的载体基板时取“载板”为译名,下同;对于封装载板中的一部分功能层,如中介层,则采用“基板”作为区分。

*高密度互连PCB电路板,即HDI电路板,high-density interconnect,相比传统电路板拥有更小的尺寸和线宽,从而在更小的面积和体积等实现更复杂的电路连通,常用于手机等对空间要求严苛的电子设备中。

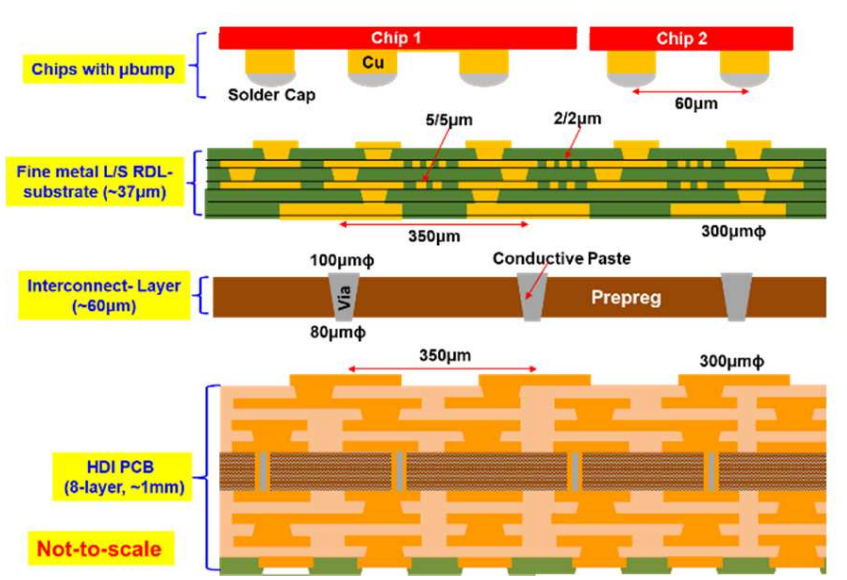

本研究成果中所采用的互连层厚度为60μm,由β级的预浸料和填充导电浆料的通孔(顶部直径为100μm,底部直径为80μm)组。

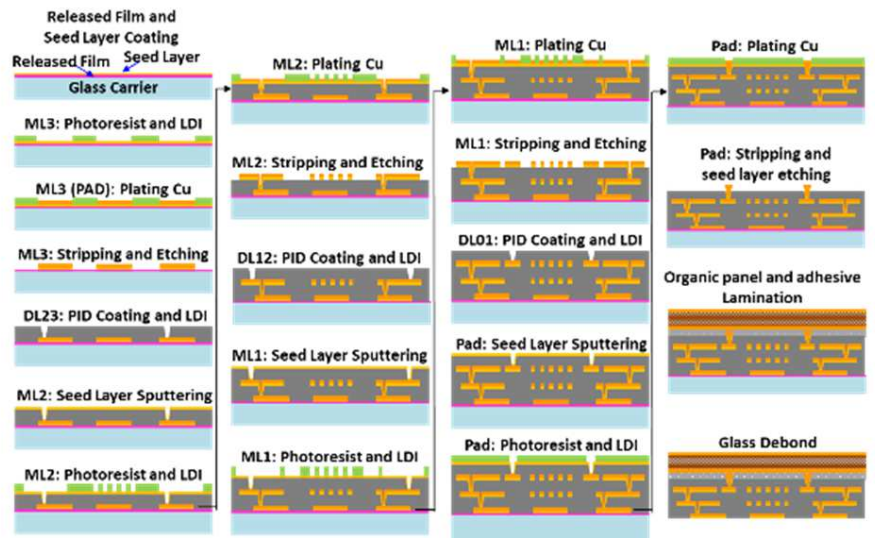

37μm无核芯基板(即中介层基板)由PID感光型电介质-LDI直写光刻-显影-PVD沉积-光刻胶上胶-LDI直写光刻-镀铜等一系列工艺步骤制备而成。

研究所用的HDI电路板厚度为1mm,共8层,焊盘间距为350um,焊盘直径为300um。

互连层、中介层和HDI这3个分离制作的结构最终通过热压缩实现完全固化一体。

以下图注中的RDL基板即为中介层部分,RDL即Re-Distribution Layer,重新布线之意,通过中介层可将原本芯片I/O点进行中介转接、使芯片能适应不同封装形式,因而得名。

已封装芯片的俯视图和剖面示意图

测试载板的几个核心部分

制作RDL基板的核心工艺步骤

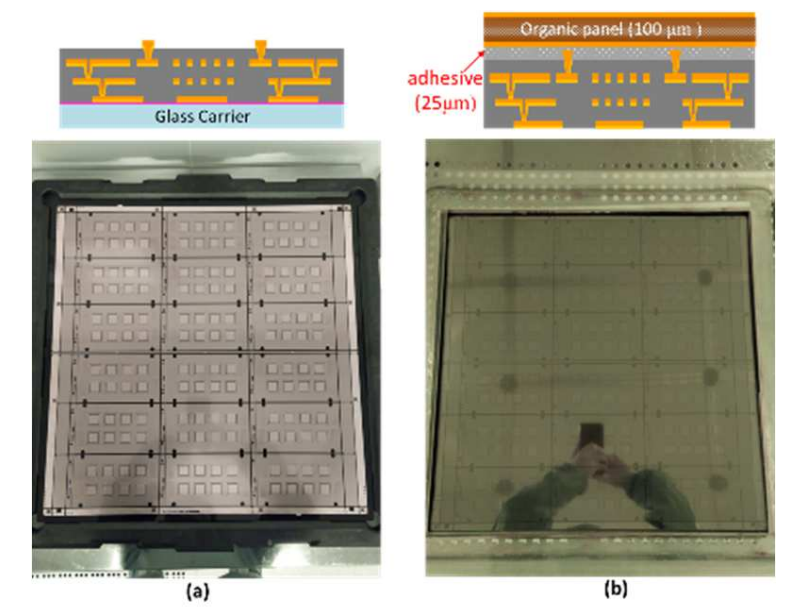

制作RDL基板的玻璃基底(a) 无玻璃基底工艺的有机面板(b)

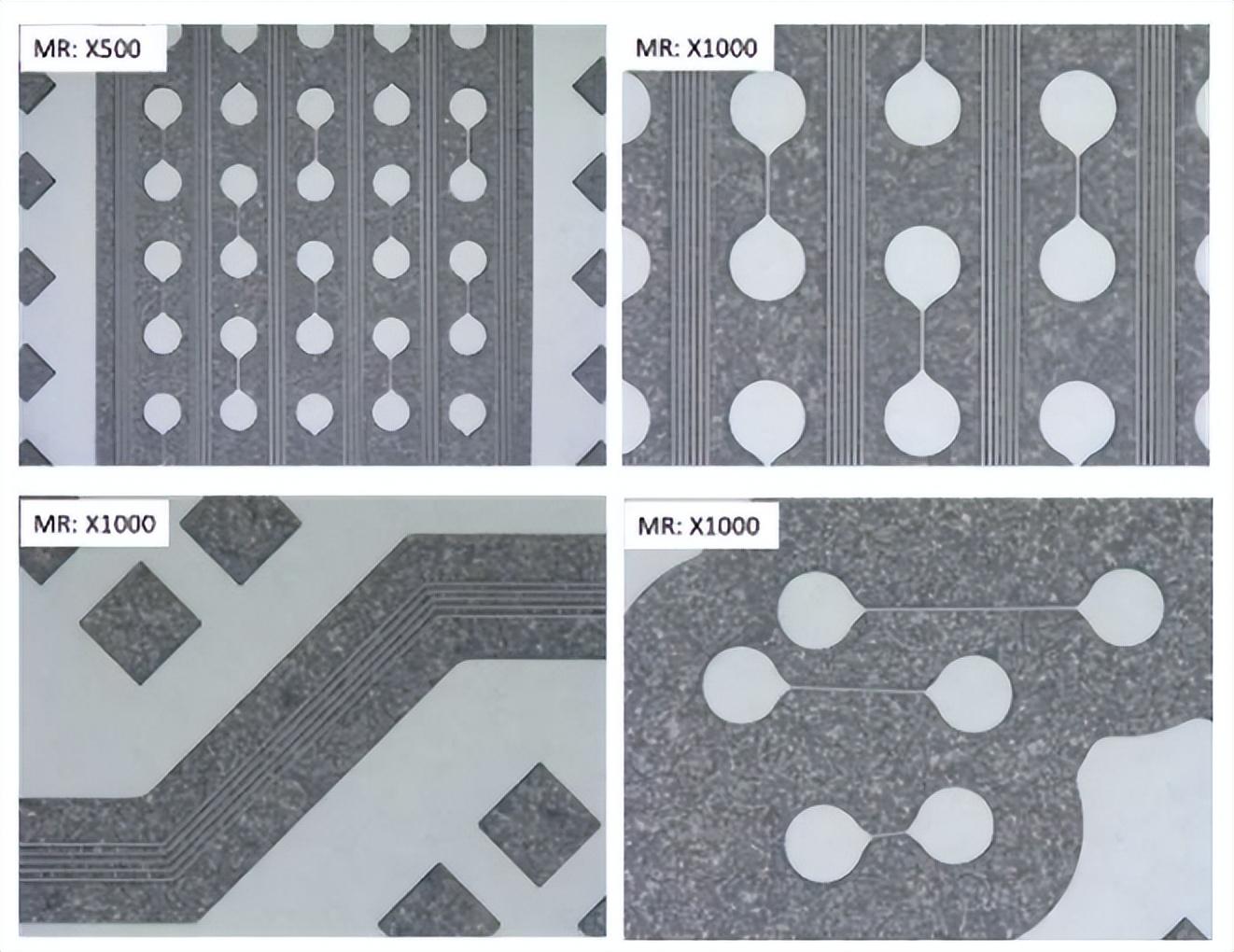

RDL基板顶部光学图像

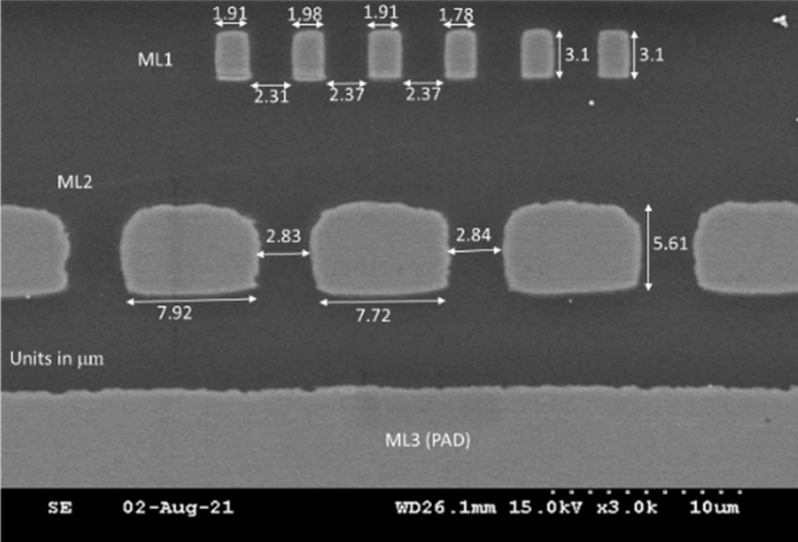

RDL基板的横截面SEM形貌像

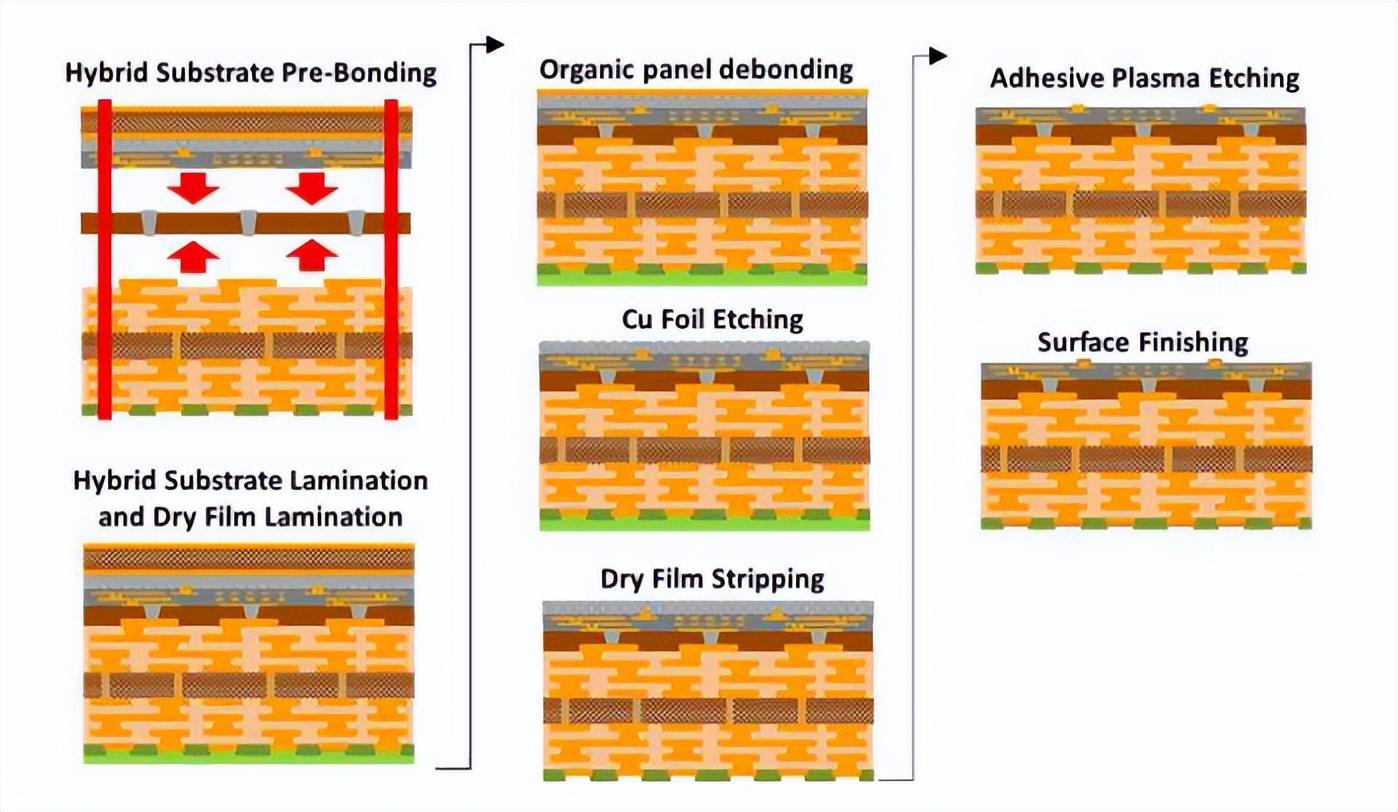

混合载板制成工艺步骤示意图

在集成电路制造领域和先进封装技术不断发展的同时,高密度IC封装载板的产能和技术发展成为了先进芯片实现产业化链条上的又一个需要突破的技术难点,产业上下游环环相扣。如今封装载板越来越多使用与IC制造相似(但精度相对要低,为微米级)的工艺,这也愈发显现了先进封装的重要性,为此ABF载板与日本食品公司味之素也频频出现在产业新闻中,高密度、高良率的精密封装载板将成为先进封装技术发展一大驱动力量。

欣兴电子成立于1990年,总公司位于台湾桃园,为联电责任企业群之一,是先进手机HDI板及IC封装载板的主要供应商。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。